Choices, choices…

There are lots of ways to do digital logic.

I choice NMOS because I wanted to.

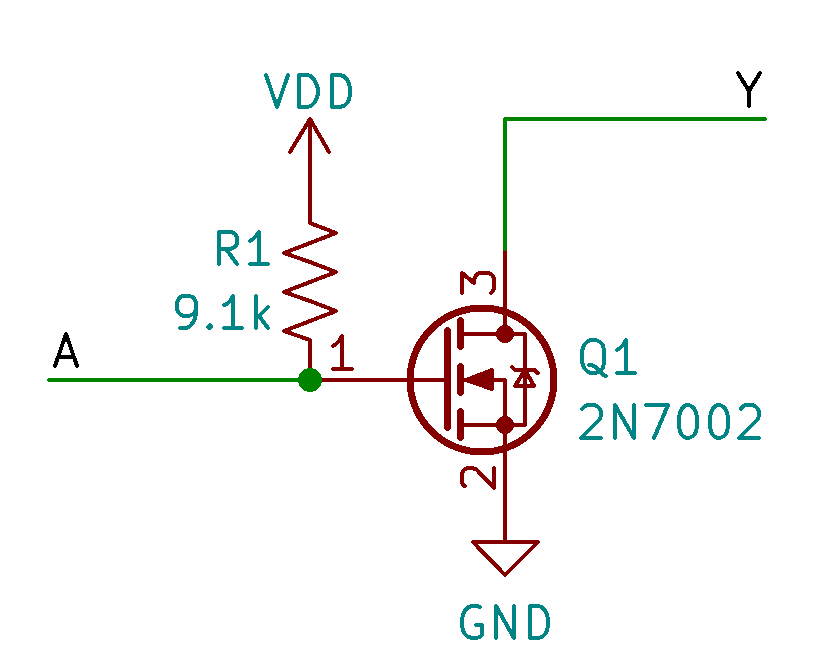

For the N-channel MOSFETs, I chose 2N7002 in SOT-23 because it was the cheapest. I ended up with 9.1k pullup resistors and 12V supply because it was convenient and seemed to be a reasonable speed compromise (a few hundred ns switching time / 16mW static power). Parts are $0.032/inverter at quanity and cover about 20mm² of board area in 0805/SOT-23.

Discrete MOSFETs with bulk connections are difficult to find and out of budget for the thousand or so that would be required, so we can’t (easily) do transmission gates and the fancy tricks they bring. Using resistors for the high side is slow and wastes power, but they are also cheap and small.

Building blocks

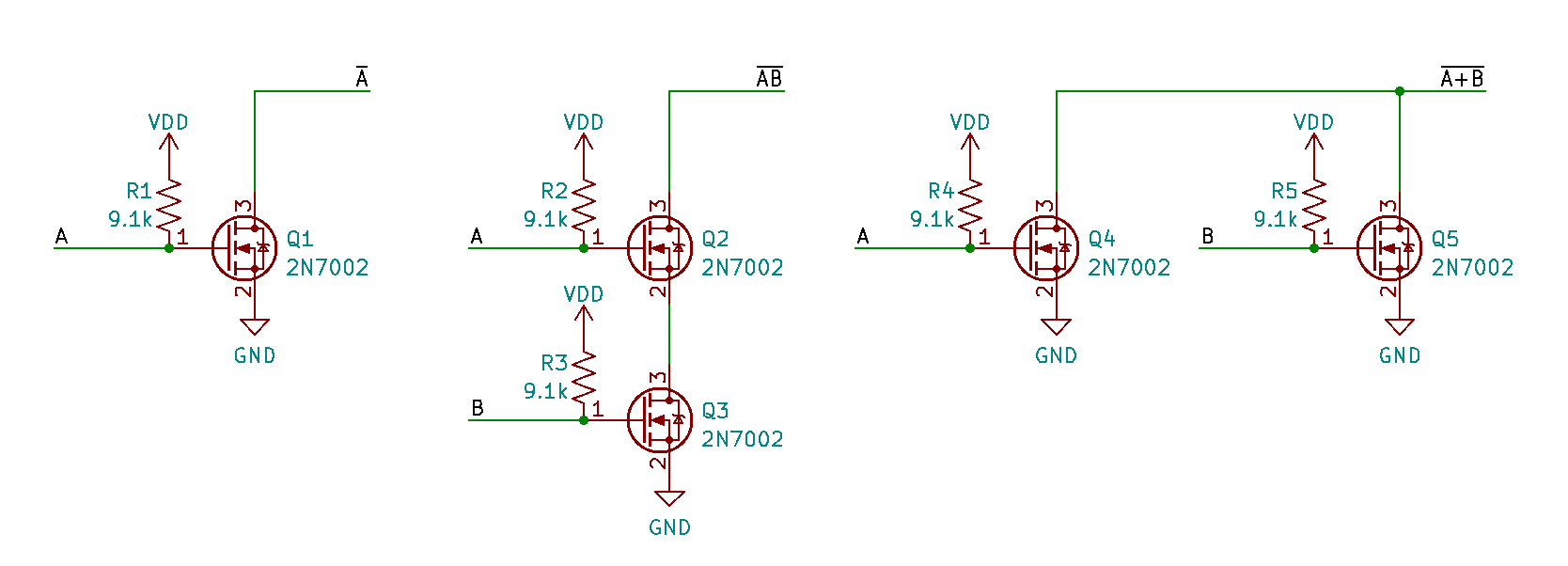

The first and simplest buliding block is the inverter. If A floats, Q conducts and pulls Y down. If A is pulled down, Q1 stops conducting and A floats. Conventionally, the pullup resistor would be shown on the output to make the state of the output obviously defined. Once you start combining many gates, this starts to cause problems with fan-out. The gate’s switching time is determined by how fast it can charge/discharge the capacitance on its output. When pulling low, the MOSFETs can go really fast, but it takes a while pulling up through the resistor. So if we want all our gates to have similar switching times, we need RC to be about the same for all of them. Most of the capacitance is in the gates of the downstream MOSFETs, so adding more MOSFETs would increase C while R remains the same. What if, instead we put a pullup at every gate? Now, adding more MOSFETs increases the capacitance, but also reduces the resistance, maintaining about the same RC.

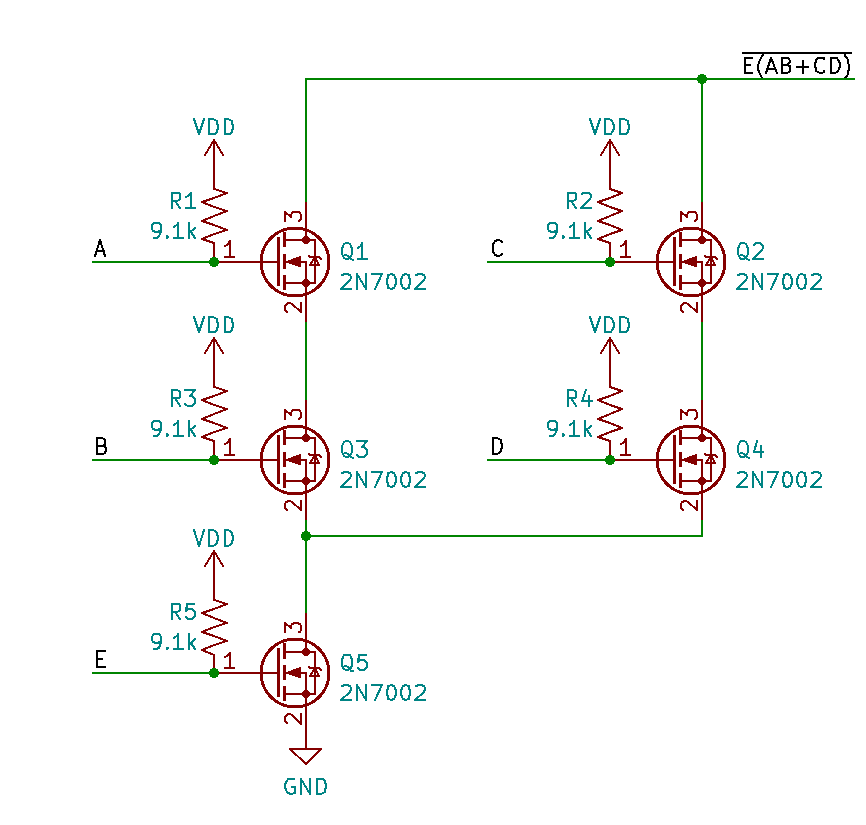

To do more interesting things, we can put the simple inverter elements in series to create a NAND gate or in parallel to create a NOR gate. Actually, we can make any combination of AND and OR with the output inverted. For example, ((AB+CD)E)’ is only one gate delay.

Optimizing logic to this form helps keep propagation delays low(er).

Optimizing logic to this form helps keep propagation delays low(er).

Conclusion

NMOS logic is bad. Don’t use it unless you’re too cheap for P-channel MOSFETs. It manages to have both horrific gate delays and riduculous static power dissipation. Oh well. It technically works.